Question Paper Set-2 Note:-Attempt questions of all sections as directed Part-1 Note:-All questions are compulsory. Each question carry 2 Marks Objective Type[2X10] 1. Translator for low level programming language were termed as A. Assembler B. Compiler C. Linker D. Loader 2. Shell is the exclusive feature of A. UNIX B. DOS C. System Software D. Application Software 3. A program in execution is called B. Instruction C. Procedure D. Function 4. Interval between the time of submission and completion of the job is called A. Waiting time B. Turnaround time C. Throughput D. Response time 5. The scheduling in which CPU is allocated to the process with least CPU burst time is called Priority Scheduling . B. Shortest Job First Scheduling C. Round Robin Scheduling D. Multilevel queue Scheduling 6. System calls are usually invoked by using A. Software interrupt B. Polling C. An indirect jump D. A privileged instruction 7. A null process has a process identifier A. -1 B. 0 C. 1 D. Null 8. CPU performance measured through A. Throughput B. MHz C. Flaps D. None 9. ..... Scheduler selects the jobs from the pool of jobs and loading to the ready queue A. Long term B. Short term C. Medium term D. None Services Inderface for Services 10 major Grand Colevice Prince Pr 10. Which scheduling policy is most suitable for a time shared operating system A. SJF B. Round Robin Part-2[8X5] Give introduction of Windows 7

UNIX

Unix is a multitasteing, multi-user compuler operating system originally developed in 1969 by a group of AT&T employees at Bell Labs, including ten Thompson, Dennis Pritchie, Brian Pernighan, Douglas McIlray

and Joe Ossanna:

The system qualifying

the resemblance

with either UNIX

Version Ton UNIX

System I are

Syslem V are Called The Toraclitional UNIX Syslems.

All others are Called UNIX

like Systèms

Company/ ATLT Bell Developer Labs

Poragrammed C

OS-family UNIX

Available

C, C++

signamor Corce!

Remal

Monolithic

User

Interface

CLI & X-Wirdow Syslem

(LINUX, IXIINIX, BSD descendanti ch.)

Peles Neumann Goics (Uniplexed Information and Computing System) Mullics (Mullipleximin information and Computer Services) gave to the name UNIX Mulliple Users.

Components Configuration of m/c clependent Partir Clevice chrivers manage ment routines [functions) header files Development/CC-C Compiler as - cissembler Icl - linker Jih - libraries Bnviroments Commande Sh - Shell Commands Utilitées - Syslem Documentation longer clocuments Waith av Singh Waith av Singh M. Tech (COMP. SC. ENGG) M. Tech (COMP. SC. ENGG)

danie mex

WINDOWS 7 DENETOBER :- MICHOSOFT Windows 7 is the latest Source Moder: Closed/shoul some rulease of Microsoft Kernel type: - Hybriel Windows, a series of STATUS :- Running Operating systems produced by Microsoft for use on pursonal compulors, including home and business desktops, Japtops, netbooks, tablet-120's and media center 120s. Windows 7 was ruleased 3 years after ill predecessor, Windows Vista. Windows 7 was intended more towards the inocemental Ulgrade to the windows line, with the goal of toeing compatible with applications and hardware with which Intindows Vista was abready compalible. Longhord -> Windows Vista Vaibravist ENGG' ENGG'

New features

1) touch and I have the singh vaibravist engg' engg'

M. Tech (COMP. SC. ENGG)

M. Tech (COMP. Sc. ENGG)

M. Tech (COMP. Sc. ENGG) 13 lackcomb -> Vienna -> Windows FM 1) touch and hand writting recognition. 2) Supposel-for visitual Hand clisks. -11 - mulli-core processors. 4) Improved boot performance Disciel-Access and Rennal improvements 6) Reclesiqued Calculator (Programmer Estatistica I) New Contral Panel [Text Toner, Display?

| 7) Window 7 includes Inder<br>Windows Media Player 12                           | nel-12xplosser 8.                    |

|---------------------------------------------------------------------------------|--------------------------------------|

| '0) Internet Spacles, Interné                                                   | 1 Backgammon                         |

| and Internel Checkers of                                                        | are relained (VISTA)                 |

| 11) Taskbox Changed taskk                                                       | sor. (Suzerhan)                      |

| 12) 13 additional Sour                                                          | od Schemes etc.                      |

| 13) Multiple Windows Cr<br>14) Melerogeneous Graphics Co<br>Physical Memory Lin | ordisconnents ordisconnents nels for |

| MINDOWS T YIERS                                                                 | ions                                 |

| VIERSION LIMIT in 32-bi                                                         |                                      |

| Windows Tultimolo                                                               | bit Windows                          |

| Windows 7 Enlaborer                                                             |                                      |

| The second secon |                            | V-3                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|

| VIERSIONI<br>Windows Tultimelle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Limit in 32-bit<br>Mindows | Limit in 64<br>bit Windows |

| Windows 7 Enleyaise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                            |

| Windows 7 Parefession                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | 192GB                      |

| Wineloues 7 Home Baric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74.3 p                     | 16 CB                      |

| Klindows 7.<br>Starler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26B                        | 8GB                        |

| States of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            | TV/A                       |

Waibhay Kant Singh M. Tech COMP, SC. ENGG! M. Tech COMP, SC. ENGG! M. T. HONOURS (COMP. SC. ENGG! M. T. S.T.

# Question1:-Solve the Readers and Writers Problem using semaphores

### **Readers Writers Problem**

A database is to be shared among several concurrent processes. Some of these processes may want only to read the database, whereas others may want to update (that is, to read and write) the database. We distinguish between these two types of processes by referring to the former as readers and to the latter as writers. Obviously, if two readers access the shared data simultaneously, no adverse affects will result. However, if a writer and some other thread (either a reader or a writer) access the database simultaneously, chaos may ensue.

To ensure that these difficulties do not arise, we require that the writers have exclusive access to the shared database. This synchronization problem is referred to as the readers—writers problem. Since it was originally stated, it has been used to test nearly every new synchronization primitive. The readers—writers problem has several variations, all involving priorities. The simplest one, referred to as the first readers—writers problem, requires that no reader will be kept waiting unless a writer has already obtained permission to use the shared object. In other words, no reader should wait for other readers to finish simply because a writer is waiting. The second readers—writers problem requires that, once a writer is ready, that writer performs its write as soon as possible. In other words, if a writer is waiting to access the object, no new readers may start reading.

A solution to either problem may result in starvation. In the first case, writers may starve; in the second case, readers may starve. For this reason, other variants of the problem have been proposed. In this section, we present a solution to the first readers—writers problem.

In the solution to the first readers—writers problem, the reader processes share the following data structures:

```

semaphore mutex, wrt;

int readcount;

```

The semaphores mutex and wrt are initialized to 1; readcount is initialized to 0. The semaphore wrt is common to both reader and writer processes. The mutex semaphore is used to ensure mutual exclusion when the variable readcount is updated. The readcount variable keeps track of how many processes are currently reading the object. The semaphore wrt functions as a mutual-exclusion semaphore for the writers. It is also used by the first or last

```

do {

wait(wrt);

// writing is performed

signal(wrt);

}while (TROF);

```

Figure The structure of a writer process.

```

do {

wait.(mutex);

readcount++;

if (readcount == 1)

wait(wrt);

signal(mutex);

// reading is performed

wait(mutex);

readcount--;

if (readcount == 0)

signal(wrt);

signal(mutex);

}

```

Figure The structure of a reader process.

reader that enters or exits the critical section. It is not used by readers who enter or exit while other readers are in their critical sections.

The code for a writer process is shown in Figure — the code for a reader process is shown in Figure —. Note that, if a writer is in the critical section and n readers are waiting, then one reader is queued on wrt, and n — 1 readers are queued on mutex. Also observe that, when a writer executes signal(wrt), we may resume the execution of either the waiting readers or a single waiting writer. The selection is made by the scheduler.

The readers—writers problem and its solutions has been generalized to provide reader—writer locks on some systems. Acquiring a reader—writer lock requires specifying the mode of the lock: either read or write access. When a process only wishes to read shared data, it requests the reader—writer lock in read mode; a process wishing to modify the shared data must request the lock in write mode. Multiple processes are permitted to concurrently acquire a reader—writer lock in read mode; only one process may acquire the lock for writing as exclusive access is required for writers.

Reader-writer locks are most useful in the following situations:

- In applications where it is easy to identify which processes only read shared data and which threads only write shared data.

- In applications that have more readers than writers. This is because readerwriter locks generally require more overhead to establish than semaphores or mutual exclusion locks, and the overhead for setting up a reader—writer lock is compensated by the increased concurrency of allowing multiple readers.

OR

Question2:-Solve the Dining Philosophers Problem using semaphores

Answer2:- **DiningPhilosopher Problem using Semaphore** Consider five philosophers who spend their lives thinking and eating. The philosophers share a circular table surrounded by five chairs each belonging to one philosophers. In the center of the table is a rice bowl, and the table is laid

Figure The situation of the dining philosophers.

with five single chopsticks (Figure —). When a philosopher thinks, she does not interact with her colleagues. From time to time, a philosopher gets hungry and tries to pick up the two chopsticks that are closest to her (the chopsticks that are between her and her left and right neighbors). A philosopher may pick up only one chopstick at a time. Obviously, she cannot pick up a chopstick that is already in the hand of a neighbor. When a hungry philosopher has both her chopsticks at the same time, she eats without releasing her chopsticks. When she is finished eating, she puts down both of her chopsticks and starts thinking again.

The dining-philosophers problem is considered a classic synchronization problem neither because of its practical importance nor because computer scientists dislike philosophers but because it is an example of a large class of concurrency-control problems. It is a simple representation of the need to allocate several resources among several processes in a deadlock-free and starvation-free manner.

One simple solution is to represent each chopstick with a semaphore. A philosopher tries to grab a chopstick by executing a wait() operation on that semaphore; she releases her chopsticks by executing the signal() operation on the appropriate semaphores. Thus, the shared data are

## semaphore chopstick[5];

where all the elements of chopstick are initialized to i. The structure of philosopher i is shown in Figure

Although this solution guarantees that no two neighbors are eating simultaneously, it nevertheless must be rejected because it could create a deadlock. Suppose that all five philosophers become hungry simultaneously and each grabs her left chopstick. All the elements of chopstick will now be equal to 0. When each philosopher tries to grab her right chopstick, she will be delayed forever.

Allow at most four philosophers to be sitting simultaneously at the table.

```

do {

wait(chopstick[i]);

wait(chopstick[(i+1) % 5]);

// eat

signal(chopstick[i]);

signal(chopstick[(i+1) % 5]);

// think

}while (TRUE);

```

Figure The structure of philosopher i

- Allow a philosopher to pick up her chopsticks only if both chopsticks are available (to do this she must pick them up in a critical section).

- Use an asymmetric solution; that is, an odd philosopher picks up first her left chopstick and then her right chopstick, whereas an even philosopher picks up her right chopstick and then her left chopstick.

Finally, any satisfactory solution to the dining-philosophers problem must guard against the possibility that one of the philosophers will starve to death. A deadlock-free solution does not necessarily eliminate the possibility of starvation.

### Unit-3

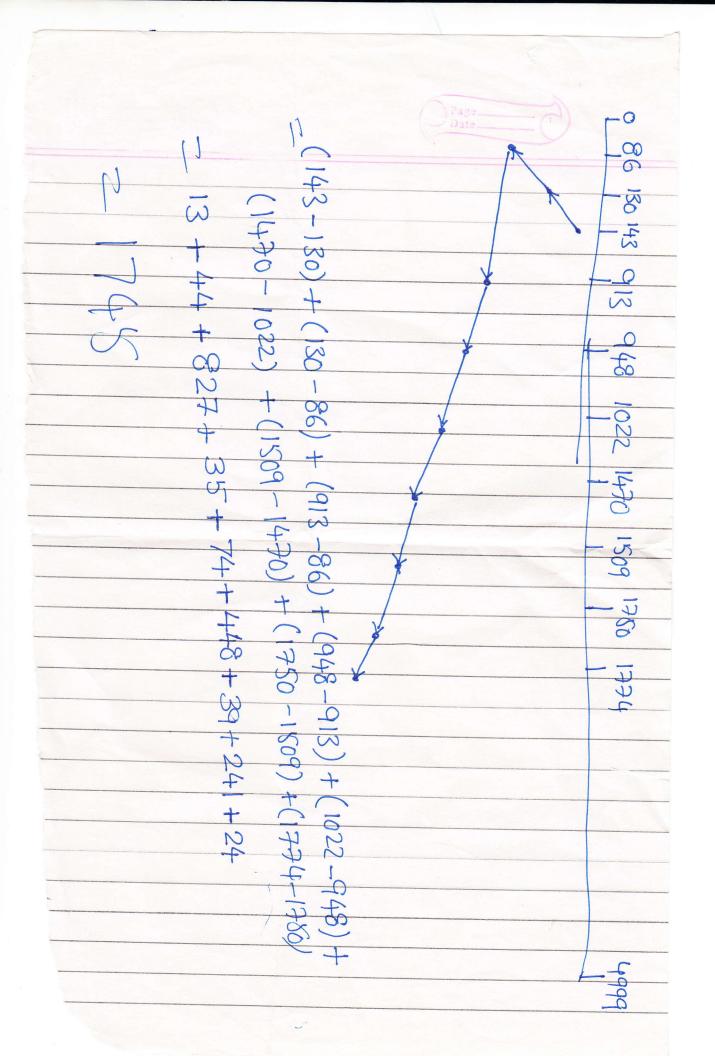

Question1:-Suppose that a disk drive has 5000 cylinders, numbered 0-4999. The drive is currently serving a request at cylinder 143 and the previous request was at cylinder 125. The queue of pending request in FIFO order is:

86, 1470, 913, 1774, 948, 1509, 1022, 1750, 130

Starting from the current head position, what is the total distance that the disk arm moves to satisfy all the pending results for each of the following disk scheduling algorithms:-

- 1. FCFS

- 2. SSTF

OR

86, 1470, 913, 1774, 948, 1509, 1022, 1750, 130 0 86 130 143 913 948 1022 1470 1509 1750 1774 4999 (143-86) + (1470-86) + (1470-913) + (1774-913) +(1774 - 948) + (1509 - 948) + (1509 - 1022) + (1750 - 1022) +(1750 - 130)57 + 1384+ 557 + 861 + 826 + 561 + 487 +728+1620 4733+728+1620 7081

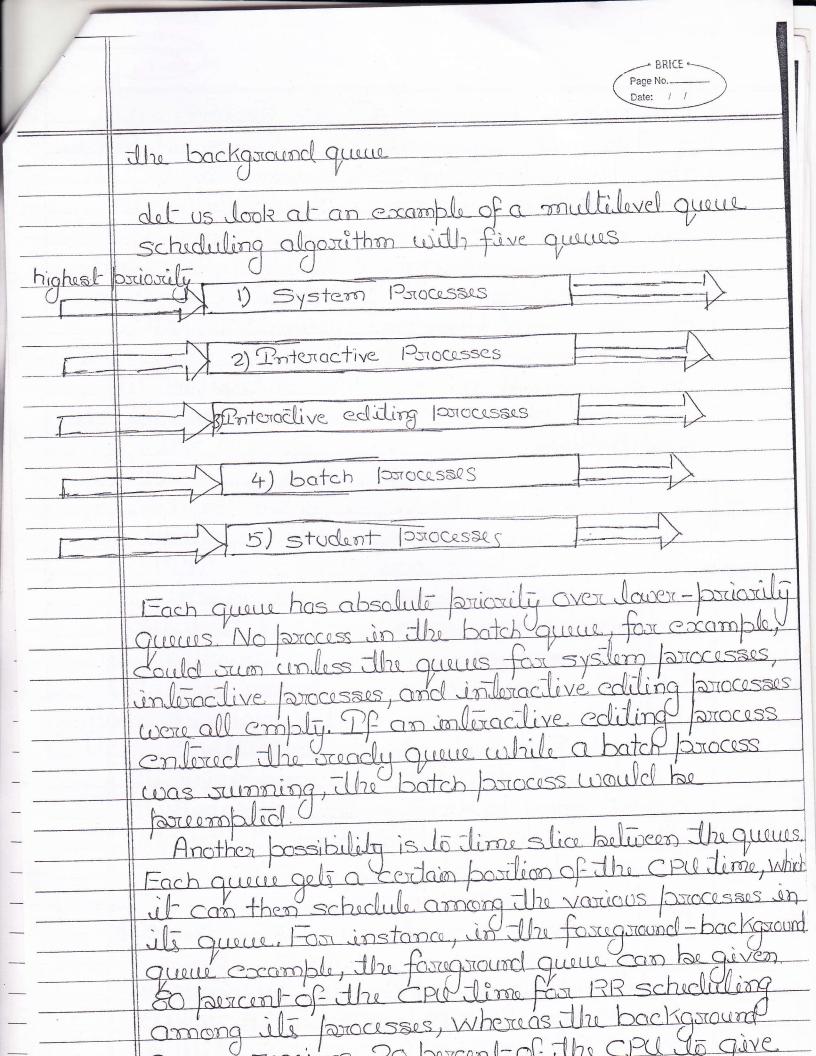

Explain Multilevel queue Scheduling and Multile feedback queue Scheduling? Give algorithm evertings in techniques? Explain Multiprocessor Scheduling In Di MULTILEVEL QUEUE SCHEDULING Another class of scheduling algorithm has been created for situations in which processes are easily classified into different groups. For example a common division is made between foreground (interactive) processes and background (bottch) processes. These two types of yarocesses have different response - lime requirements, and so might have different scheduling needs. In addition, forground processes may have parioxily (externally defined) over background processes multilevel queue-scheduling algorithm separate queues. The processes are permanently assigned to one queue, generally based on some proporty of the process such as memory size, process priority, or process ly se l'Each queue has ils algorithm, Fox example, separate queues roght be used for foreground and background processes. The foreground queue might be scheduled by an PRR algorithm, While the background queue is Scheduled by an algorathm (wordidolid) In addition, there must be scheduling between the queies, which is commonly implemented as a fixed-prioxity preemptive. scheduling. For example the foreground

MULTILEVEL FEEDBACK QUEUF SCHEDULING Mosmally, in a multilevel queue scheduling algorithm, processes are permanent assigned to a queue on entry. Processes do not move There are separate queues for foreground and background processes, for example, do not move form one queue l'o The other, Since processes do not change their foreground Our background nature. This setub has advantage of low scheduling overthead, but is inflexible Multilevel Feedback queue scheduling, however, allows a process de move beliveen queues à sebarate bracesses with characteristics. much CPU dime, il will be moved to a lower-priority queue interactive processes in the higher-priority queues. Similarly, a process Uthaltoo long Vin a lower-priorite elle may be moved to a higherqueue This form of aging stavalion Tox example, consider a multilevel feedback

Tox example, consider a multilevel feedback queue schedular with three queues, numbered from 0 to 2. The scheduler first executes all processes in queue 0.

> quantum 8 execule processes in queue 1. Similarly, processes in queue 2 will only be executed if queues O and 1 de emply. A Brocess That arrives for queue 1 will preedopt a process in queue? A process in queue 1 will in turn be preempted by a process aviving for queue o. A process enliving the ready queue is put in queue O. A process in queue O'is given a time quantum of 8 milliseconds. To it closs not finish will all this time, it is moved to the Jail of queue 1. Pf queue 0 is emply the process at the head of queue 1 is given a quantum of 16 milliseconds. If it closs not complete, it is preempted and is put into Queue 2. Processes in queue 2 are ruis on an FCFS basis, only when queues O and 1 are emply 'IRis scheduling algorithm gives highest priorily to any process Unitly a CPU burst of 8 milliseconds or less. Such a process will quickly get the CPU finish its CPU burst, and go off I/O burst. Processes That need more than 8, but less than 24, milliseconds are also served quickly, although with lower priority than starler processed Long processes automatically sink to queue 2 and like served in FCFS ander with any CPU cycles left over from queues O and

|   | Por general, a multilevel f-eedback queue schedular is defined by the following parameters:   |

|---|-----------------------------------------------------------------------------------------------|

| 1 | The number of queues.                                                                         |

| 2 | The scheduling algorithm for each                                                             |

| 3 | The method used to determine when to upgrade a process to a higher positionity queue          |

| 4 | Re method used to determine when to demote a process to a lower-priority                      |

| 5 | Re method used to determine which queue a process will enter when that process needs service. |

|   |                                                                                               |

# MULTIPLE PROCESSOR SCHEDULING

Pf multiple CPUs are available, the scheduling problem is corouspondingly more complex. Many possibilities have been tried and as we saw with single processor CPU scheduling, there is no one best solution. We concentrate on systems where the processors are identical (homogeneous) in terms of their functionality; Any available processor can then be used the run any processor can the queue

Even within homogeneous multiprocessor, there are sometimes limitations on scheduling Consider a system with an T/o device attached to a private bus of one processor Processes wishing to use that device must be scheduled to sun on that processor. Processes wishing to use that device must be scheduled to sun on that processor, Processes wishing to use that device must be scheduled to sun on that processor, otherwise the device would not be available.

available, then load sharing can occur. It would be possible to provide a separate queue for each processor. In this case however, one processor could be idle, with an emply queue while another processor was very busy. To prevent this situation.

we use a common ready queue. All processes go into one queue and are scheduled onto any available processor

In such a scheme, one of live scheduling approaches may be used Pn one approach, approach, approach processor examines the common bready queue and selects a process to execute. The we have multiple processors trying to access and update a common data estructures, each processor must be programmed very carefully we must ensure that two processors do not choose the same process, and that processes are not lost forom the queue. The other approach avoids this problem by appointing one processor as schedular for the other processors, thus creating a moster-slave structure.

Some systems coon this structure one step further, by having all scheduling decisions I/O processing, and other system activities handled by one single processor the master server. The other processors only execute user code. This asymmetric multiprocessing is for simpler than symmetric multiprocessing because only one processor accesses the system data structures, alleviating the need for data showing.

ALGORITHM EVALUATION To select an algorithm, we must first define The relative importance of these measures. Our critéria may include several measures, such as Maximize che utilization under the constraint That The maximum response lime is 1 second Maximize throughput such that turnaround time is (on average) linearly proportional to There are a number of different evaluation methods given below: Deterministic Modeling Queueing Models Simulations [Pm/slementation Deterministic Modeling One major class of evaluation methods is called analytic evaluation. Analytic evaluation uses the given algorithm and the Bystem workload to Uproduce Va formula ar number that evaluales the performance of the algorithm for that woodsload One type of malytic evaluation is deterministic modeling. This method takes a particular performance of each algorithm for that

workload

Deterministic modeling is simple and fast.

It gives exact numbers for infact, and its answers apply to only those cases.

The main uses of deterministic modeling are in describing scheduling algorithms of and providing texamples. In cases where we may be trunning the same programs over and over again, and can measure the program's processing requirements exactly we may be able to use deterministic modeling to select a scheduling algorithm.

Queueing Models

The Compuler system is described as a network of servers. Fach server has a queue of waiting processes. The CPV is a server with its ready queue as is the I/O system with its of service queues knowing arrival rates and service trates, we can compute utilization, average queue length, average wait-time and so on. This area of study is called queueing-network analysis.

As an example, let n bettre average queue length (excluding the possocies being serviced). The possocies being serviced time

in the queue, and let & be the average.

arrival rate for new processes in the

queue (such as three processes per second).

Then we expect that during the time W

that a process waits, &x W new processes

will covive in the queue If the system is

in a steady state, then the number of

processes leaving the queue must be equal to

the number of processes that covive Thus,

n = > x W diltes formula

Rect a more accurate evaluation of scheduling algorithms we can use simulations. Simulations of involve programming a model of the computer system. Software data structures represent The major components of the system. The simulator has a variable representing a clock; as this variable's value is increased, the simulator modifies the system state to reflect the activities of the devices, the processes, and the schedular As the simulation executes, statistics that indicate algorithm performance are gallrered and positive.

The data to drive the simulation can be generaled in several ways. The most common method uses a transforment to generater, which is programmed to generate processes, cold burst times arrivals, departures and so on, according to probability distributions. The distributions may be defined mathematically or empirically. To the distribution dis to be defined empirically, measurements of the actual system which study are taken.

The tresults are used to define the actual distribution of events in the real system, and this distribution can then be used to chrive the simulation.

A distribution-chriven simulation

may be inaccurate, however, due to

relationships between successive events

in the real system. The frequency

distribution indicates only how many

of each event occur, it does not

indicate anything about the order

of their occurrence. To covered this

broblem, we as use trace tapes we

create a trace tape by monitoring the

real system, recording the sequence

of actual events. This sequence is then used

to chive the simulation. Trace tapes provide

an excellent way to compare two algorithms

on exactly the same set of real inputs. This

BRICE -Acholad Date: Simulations can be expensive; however, often ocequiring hours of computer time more detailed simulation provides more accurate results, but also requires more compuler lime. In addition, torace tapes can require large amounts o storage slace! Finally, the design cooling and debugging of the smulaloup Simulation CPU 16 I/0 213 CPU 12 actual Flar I/01/2 Droces Simulation execulor CPU 2 I/O 147 SJF CPU 173 Simulation IMPLEMENTATION simulation is of limited accuracy The only combletely accurate Schedelling o system and ā 200 actial algorithm Cipporoach System for evalua operaling conclidions

The major difficulty is the cost-us approach. The expense, is incur

Question1:-Explain Process Termination and Resource Preemption in deadlock recovery?

# Recovery From Deadlock

When a detection algorithm determines that a deadlock exists, several alternatives are available. One possibility is to inform the operator that a deadlock has occurred and to let the operator deal with the deadlock manually. Another possibility is to let the system *recover* from the deadlock automatically. There are two options for breaking a deadlock. One is simply to abort one or more processes to break the circular wait. The other is to preempt some resources from one or more of the deadlocked processes.

## **Process Termination**

To eliminate deadlocks by aborting a process, we use one of two methods. In both methods, the system reclaims all resources allocated to the terminated processes.

- \* Abort all deadlocked processes. This method clearly will break the deadlock cycle, but at great expense; the deadlocked processes may have computed for a long time, and the results of these partial computations must be discarded and probably will have to be recomputed later.

- Abort one process at a time until the deadlock cycle is eliminated. This method incurs considerable overhead, since, after each process is aborted, a deadlock-detection algorithm must be invoked to determine whether any processes are still deadlocked.

Aborting a process may not be easy. If the process was in the midst of updating a file, terminating it will leave that file in an incorrect state. Similarly, if the process was in the midst of printing data on a printer, the system must reset the printer to a correct state before printing the next job.

If the partial termination method is used, then we must determine which deadlocked process (or processes) should be terminated. This determination is a policy decision, similar to CPU-scheduling decisions. The question is basically an economic one; we should abort those processes whose termination will incur the minimum cost. Unfortunately, the term *minimum cost* is not a precise one. Many factors may affect which process is chosen, including:

- 1. What the priority of the process is

- 2. How long the process has computed and how much longer the process will compute before completing its designated task

- 3. How many and what type of resources the process has used (for example, whether the resources are simple to preempt)

- 4. How many more resources the process needs in order to complete

- 5. How many processes will need to be terminated

- 6. Whether the process is interactive or batch

# Resource Preemption

To eliminate deadlocks using resource preemption, we successively preempt some resources from processes and give these resources to other processes until the deadlock cycle is broken.

If preemption is required to deal with deadlocks, then three issues need to be addressed:

- 1. Selecting a victim. Which resources and which processes are to be preempted? As in process termination, we must determine the order of preemption to minimize cost. Cost factors may include such parameters as the number of resources a deadlocked process is holding and the amount of time the process has thus far consumed during its execution.

- 2. Rollback. If we preempt a resource from a process, what should be done with that process? Clearly, it cannot continue with its normal execution; it is missing some needed resource. We must roll back the process to some safe state and restart it from that state.

Since, in general, it is difficult to determine what a safe state is, the simplest solution is a total rollback: Abort the process and then restart it. Although it is more effective to roll back the process only as far as necessary to break the deadlock, this method requires the system to keep more information about the state of all running processes.

3. Starvation. How do we ensure that starvation will not occur? That is, how can we guarantee that resources will not always be preempted from the same process?

In a system where victim selection is based primarily on cost factors, it may happen that the same process is always picked as a victim. As a result, this process never completes its designated task, a starvation situation that must be dealt with in any practical system. Clearly, we must ensure that a process can be picked as a victim only a (small) finite number of times. The most common solution is to include the number of rollbacks in the cost factor.

# Eplain Combined with Applications to proposed oct hand with the state of the state

WEDNESDAY

CONTRINED AISTROACH TO DIEADLOCK

method is based on the notion that prevention, avoidance and detection) alone classes that are technique for handling deadlacks Corderad is applied to the classes. plessaches, allowing the use of the plessach of four each class Oresearchers to carollaine The Three Scients Sciente (0) resource -allication and sale of the coline or sections pasic approaches have argued that more of JUSOUNCE - ON Clering technique Historichically One problems carcounting handling chadlocks Dasic ! Juli bidiseoc

System that casy to Show that a system that complains this strategy will not be subjected to chacklacks.

Includ, a chacklock cannot involve more than one class, since the system class, since the within each class one of the basic abox caches is used. Consequent the system is not subject to the chack of the system is not subject. To

215-150

THUR

AUGU

a system that consists of the consists of the

100 \* Indurnal Presources

as a process control block.

\* Central Memory

Memory used by a user Joh

\* Job Pesources

Assignable devices (such as a talse

Obrine) and filles.

\* Swappable Space

Space for each user job on t

FRIDAY

One, austin oxders the classes as shown, do cada class: Jand usis The mixed deadlock solution for this supposed of businostics

12.00 \* (Indianal Brevention Wisiough suspource Jackention Maid State Jum - Time () houces are necessary. Desugar panding reguests 19esources:-

me morely. Jawentien Urraugh be used, wince Swalpace Out Can, |Yemoxy :a job can always ariemalic

Chypiclemic Can be used information needed vioquerements can be CB0 1010 - Contact Cards LO SOLVICES about Jusquice abtained from since The

are usually schown usicaments Swalphable Space Used 1200mg Since

217-148

AUGUS

Solution of the deadlack me hosic alporaches can be within the forgine words of oresource above example shows how you obtain an effective arolalera. misced SATUR

WORKING of COMBINED AIDPROACH

Types on the bases of workinged into Collowing Sel-of-U Classes The this apparach all the System Ulan Chrese resource De armanged into Sulabal Th cosource Ty as are the ousource

6.00 5 183, 185, 186 3 & 192, 184, 1893

1

DISTORDING be conthe the Dasis Posis of heuricalcal Conalid Dentain Caite Classes on ondin mo

9.00 P MONDAY AUGUST '06. 7, 1 RIO 219-146 WHY-1 MO TU WE TH FR SA SU

31 1 2

) 1.00

02

192, 194, 199

10.00

0 193, 195, R8

Mulologe

Classes C1, C2, C3, C4

たと

in the fish

given tashion

TOTOLO O Proposice of hen Two Count tham apour, wal radease Departor Driocess in bjudge Lesourice Judiase 128 + Han Onl indli, vidua Signo commence of Standa Dics it is "holding O MOCO Stadings pulaço Oh, increasing clotection. sugues/any of the lifferent Classes andcess, ica of resoince are tallen in SELL DEMOSOR is made 031 ion. 13ul, 12 It rations RACEC 20mes Otto Than

CIOUBUSA

100

SSOOM

CPU

LAS

Simol Nol

THAST

Seguence

1-

S-Establisher 18 19 20-21 22 28 24 P Col FLIE C 9 700 ... 10.00 Operating system. By switching 1100 Can Umake The DISEED 002 2.00 4.00 among Warrocesses, CITY Schoduling Othor CIOU sphiduling Sef: Strange SSIDORG Osci OL D MADIC OCCOMPANSAMO Captullion H/O STUDO CONCEPTS Day agmondo Burst-1000 a somodos STOCES Jestma S SSIDONE 3 core sylve reging lados The obserating system WEEK 33 220-145 the basis of mullipar DOLLOC or my pural xxhetus, u babobed belinger whe 1 CYCL (STC) callled 0300 Dollar SU SSIJONA Bulletral VIVE amocess 10 @ Demalion Span police of SSissoid viceth naos 5017 7

2006 - 5-th 20 9 2010 Manday

Dalet

Total Total student :-Total

AUG

5,4

Absent-:-- morend

Question1:-Explain Virtual Memory?

Virtual memory is a technique that allows the execution of processes that are not completely in memory. One major advantage of this scheme is that programs can be larger than physical memory. Further, virtual memory abstracts main memory into an extremely large, uniform array of storage, separating logical memory as viewed by the user from physical memory. This technique frees programmers from the concerns of memory-storage limitations. Virtual memory also allows processes to share files easily and to implement shared memory. In addition, it provides an efficient mechanism for process creation. Virtual memory is not easy to implement, however, and may substantially decrease performance if it is used carelessly.

# Background

The memory-management algorithms outlined are necessary because of one basic requirement: The instructions being executed must be in physical memory. The first approach to meeting this requirement is to place the entire logical address space in physical memory. Dynamic loading can help to ease this restriction, but it generally requires special precautions and extra work by the programmer.

The requirement that instructions must be in physical memory to be executed seems both necessary and reasonable; but it is also unfortunate, since it limits the size of a program to the size of physical memory. In fact, an examination of real programs shows us that, in many cases, the entire program is not needed. For instance, consider the following:

- Programs often have code to handle unusual error conditions. Since these errors seldom, if ever, occur in practice, this code is almost never executed.

- Arrays, lists, and tables are often allocated more memory than they actually need. An array may be declared 100 by 100 elements, even though it is seldom larger than 10 by 10 elements. An assembler symbol table may have room for 3,000 symbols, although the average program has less than 200 symbols.

- Certain options and features of a program may be used rarely. For instance, the routines on U.S. government computers that balance the budget are only rarely used.

Even in those cases where the entire program is needed, it may not all be needed at the same time.

The ability to execute a program that is only partially in memory would confer many benefits:

A program would no longer be constrained by the amount of physical memory that is available. Users would be able to write programs for an extremely large virtual address space, simplifying the programming task.

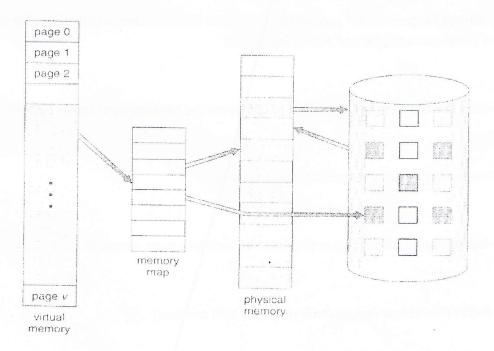

Figure Diagram showing virtual memory that is larger than physical memory.

- Because each user program could take less physical memory, more programs could be run at the same time, with a corresponding increase in CPU utilization and throughput but with no increase in response time or turnaround time.

- Less 1/O would be needed to load or swap each user program into memory, so each user program would run faster.

Thus, running a program that is not entirely in memory would benefit both the system and the user.

Virtual memory involves the separation of logical memory as perceived by users from physical memory. This separation allows an extremely large virtual memory to be provided for programmers when only a smaller physical memory is available (Figure ). Virtual memory makes the task of programming much easier, because the programmer no longer needs to worry about the amount of physical memory available; she can concentrate instead on the problem to be programmed.

The virtual address space of a process refers to the logical (or virtual) view of how a process is stored in memory. Typically, this view is that a process begins at a certain logical address—say, address 0—and exists in contiguous memory, as shown in Figure , though, that in fact physical memory may be organized in page frames and that the physical page frames assigned to a process may not be contiguous. It is up to the memory-management unit (MMU) to map logical pages to physical page frames in

Note in Figure — that we allow for the heap to grow upward in memory as it is used for dynamic memory allocation. Similarly, we allow for the stack to grow downward in memory through successive function calls. The large blank space (or hole) between the heap and the stack is part of the virtual address

Figure Virtual address space.

space but will require actual physical pages only if the heap or stack grows. Virtual address spaces that include holes are known as **sparse** address spaces. Using a sparse address space is beneficial because the holes can be filled as the stack or heap segments grow or if we wish to dynamically link libraries (or possibly other shared objects) during program execution.

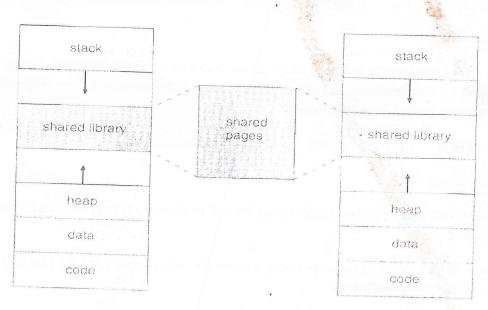

In addition to separating logical memory from physical memory, virtual memory also allows files and memory to be shared by two or more processes through page sharing

This leads to the following benefits:

- System libraries can be shared by several processes through mapping of the shared object into a virtual address space. Although each process considers the shared libraries to be part of its virtual address space, the actual pages where the libraries reside in physical memory are shared by all the processes

Typically, a library is mapped read-only into the space of each process that is linked with it.

- similarly, virtual memory enables processes to share memory. Recall that two or more processes can communicate through the use of shared memory. Virtual memory allows one process to create a region of memory that it can share with another process. Processes sharing this region consider it part of their virtual address space, yet the actual physical pages of memory are shared, much as is illustrated in Figure

- Virtual memory can allow pages to be shared during process creation with the fork() system call, thus speeding up process creation.

We will further explore these—and other—benefits of virtual memory later in this chapter. First, we begin with a discussion of implementing virtual memory through demand paging.

Figure Shared library using virtual memory.

# Question2:-Describe Demand Paging?

Consider how an executable program might be loaded from disk into memory. One option is to load the entire program in physical memory at program execution time. However, a problem with this approach is that we may not initially need the entire program in memory. Consider a program that starts with a list of available options from which the user is to select. Loading the entire program into memory results in loading the executable code for all options, regardless of whether an option is ultimately selected by the user or not. An alternative strategy is to initially load pages only as they are needed. This technique is known as demand paging and is commonly used in virtual memory systems. With demand-paged virtual memory, pages are only loaded when they are demanded during program execution; pages that are never accessed are thus never loaded into physical memory.

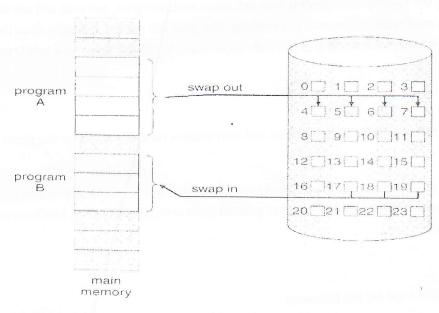

A demand-paging system is similar to a paging system with swapping (Figure ) where processes reside in secondary memory (usually a disk). When we want to execute a process, we swap it into memory. Rather than swapping the entire process into memory, however, we use a lazy swapper. A lazy swapper never swaps a page into memory unless that page will be needed. Since we are now viewing a process as a sequence of pages, rather than as one large contiguous address space, use of the term swapper is technically incorrect. A swapper manipulates entire processes, whereas a pager is concerned with the individual pages of a process. We thus use pager, rather than swapper, in connection with demand paging.

Figure Transfer of a paged memory to contiguous disk space.

# **Basic Concepts**

When a process is to be swapped in, the pager guesses which pages will be used before the process is swapped out again. Instead of swapping in a whole process, the pager brings only those necessary pages into memory. Thus, it avoids reading into memory pages that will not be used anyway, decreasing the swap time and the amount of physical memory needed.

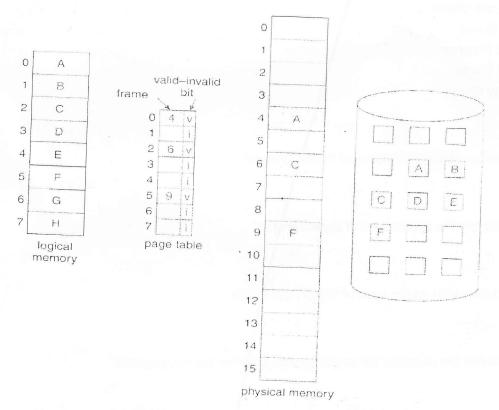

With this scheme, we need some form of hardware support to distinguish between the pages that are in memory and the pages that are on the disk. The valid-invalid bit scheme described This time, however, when this bit is set to "valid," the associated page is both legal and in memory. If the bit is set to "invalid," the page either is not valid (that is, not in the logical address space of the process) or is valid but is currently on the disk. The page-table entry for a page that is brought into memory is set as usual, but the page-table entry for a page that is not currently in memory is either simply marked invalid or contains the address of the page on disk. This situation is depicted in Figure

Notice that marking a page invalid will have no effect if the process never attempts to access that page. Hence, if we guess right and page in all and only those pages that are actually needed, the process will run exactly as though we had brought in all pages. While the process executes and accesses pages that are memory resident, execution proceeds normally.

**Figure** Page table when some pages are not in main memory.

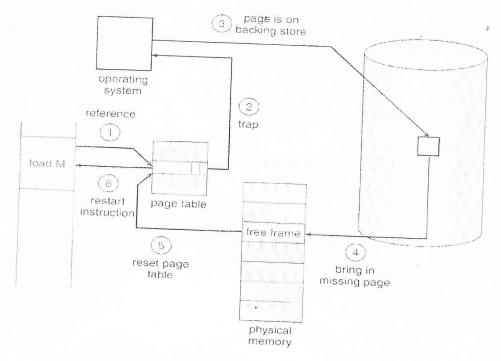

Figure Steps in handling a page fault.

But what happens if the process tries to access a page that was not brought into memory? Access to a page marked invalid causes a **page-fault trap**. The paging hardware, in translating the address through the page table, will notice that the invalid bit is set, causing a trap to the operating system. This trap is the result of the operating system's failure to bring the desired page into memory. The procedure for handling this page fault is straightforward (Figure ):

- 1. We check an internal table (usually kept with the process control block) for this process to determine whether the reference was a valid or an invalid memory access.

- 2. If the reference was invalid, we terminate the process. If it was valid, but we have not yet brought in that page, we now page it in.

- 3. We find a free frame (by taking one from the free-frame list, for example).

- 4. We schedule a disk operation to read the desired page into the newly allocated frame.

- 5. When the disk read is complete, we modify the internal table kept with the process and the page table to indicate that the page is now in memory.

- 6. We restart the instruction that was interrupted by the trap. The process can now access the page as though it had always been in memory.

In the extreme case, we can start executing a process with no pages in memory. When the operating system sets the instruction pointer to the first

instruction of the process, which is on a non-memory-resident page, the process immediately faults for the page. After this page is brought into memory, the process continues to execute, faulting as necessary until every page that it needs is in memory. At that point, it can execute with no more faults. This scheme is pure demand paging: Never bring a page into memory until it is required.

Theoretically, some programs could access several new pages of memory with each instruction execution (one page for the instruction and many for data), possibly causing multiple page faults per instruction. This situation would result in unacceptable system performance. Fortunately, analysis of running processes shows that this behavior is exceedingly unlikely. Programs tend to have locality of reference, , which results in reasonable performance from demand paging.

The hardware to support demand paging is the same as the hardware for

paging and swapping:

Page table. This table has the ability to mark an entry invalid through a valid-invalid bit or special value of protection bits.

Secondary memory. This memory holds those pages that are not present in main memory. The secondary memory is usually a high-speed disk. It is known as the swap device, and the section of disk used for this purpose is known as swap space.

A crucial requirement for demand paging is the need to be able to restart any instruction after a page fault. Because we save the state (registers, condition code, instruction counter) of the interrupted process when the page fault occurs, we must be able to restart the process in *exactly* the same place and state, except that the desired page is now in memory and is accessible. In most cases, this requirement is easy to meet. A page fault may occur at any memory reference. If the page fault occurs on the instruction fetch, we can restart by fetching the instruction again. If a page fault occurs while we are fetching an operand, we must fetch and decode the instruction again and then fetch the operand.

As a worst-case example, consider a three-address instruction such as ADD the content of A to B, placing the result in C. These are the steps to execute this instruction:

- 1. Fetch and decode the instruction (ADD).

- 2. Fetch A.

- 3. Fetch B.

- 4. Add A and B.

- 5. Store the sum in C.

If we fault when we try to store in C (because C is in a page not currently in memory), we will have to get the desired page, bring it in, correct the page table, and restart the instruction. The restart will require fetching the instruction again, decoding it again, fetching the two operands again, and

then adding again. However, there is not much repeated work (less than one complete instruction), and the repetition is necessary only when a page fault occurs.

The major difficulty arises when one instruction may modify several different locations. For example, consider the IBM System 360/370 MVC (move character) instruction, which can move up to 256 bytes from one location to another (possibly overlapping) location. If either block (source or destination) straddles a page boundary, a page fault might occur after the move is partially done. In addition, if the source and destination blocks overlap, the source block may have been modified, in which case we cannot simply restart the instruction.

This problem can be solved in two different ways. In one solution, the microcode computes and attempts to access both ends of both blocks. If a page fault is going to occur, it will happen at this step, before anything is modified. The move can then take place; we know that no page fault can occur, since all the relevant pages are in memory. The other solution uses temporary registers to hold the values of overwritten locations. If there is a page fault, all the old values are written back into memory before the trap occurs. This action restores memory to its state before the instruction was started, so that the instruction can be repeated.

This is by no means the only architectural problem resulting from adding paging to an existing architecture to allow demand paging, but it illustrates some of the difficulties involved. Paging is added between the CPU and the memory in a computer system. It should be entirely transparent to the user process. Thus, people often assume that paging can be added to any system. Although this assumption is true for a non-demand-paging environment, where a page fault represents a fatal error, it is not true where a page fault means only that an additional page must be brought into memory and the process restarted.

# Performance of Demand Paging

Demand paging can significantly affect the performance of a computer system. To see why, let's compute the **effective access time** for a demand-paged memory. For most computer systems, the memory-access time, denoted *ma*, ranges from 10 to 200 nanoseconds. As long as we have no page faults, the effective access time is equal to the memory access time. If, however, a page fault occurs, we must first read the relevant page from disk and then access the desired word.

Let p be the probability of a page fault ( $0 \le p \le 1$ ). We would expect p to be close to zero—that is, we would expect to have only a few page faults. The **effective access time** is then

effective access time =  $(1 - p) \times ma + p \times page$  fault time.

To compute the effective access time, we must know how much time is needed to service a page fault. A page fault causes the following sequence to occur:

- 1. Trap to the operating system.

- 2. Save the user registers and process state.

- 3. Determine that the interrupt was a page fault.

- 4. Check that the page reference was legal and determine the location of the page on the disk.

- 5. Issue a read from the disk to a free frame:

- a. Wait in a queue for this device until the read request is serviced.

- b. Wait for the device seek and/or latency time.

- c. Begin the transfer of the page to a free frame.

- 6. While waiting, allocate the CPU to some other user (CPU scheduling, optional).

- 7. Receive an interrupt from the disk I/O subsystem (I/O completed).

- 8. Save the registers and process state for the other user (if step 6 is executed).

- 9. Determine that the interrupt was from the disk.

- 10. Correct the page table and other tables to show that the desired page is now in memory.

- 11. Wait for the CPU to be allocated to this process again.

- 12. Restore the user registers, process state, and new page table, and then resume the interrupted instruction.

Not all of these steps are necessary in every case. For example, we are assuming that, in step 6, the CPU is allocated to another process while the I/O occurs. This arrangement allows multiprogramming to maintain CPU utilization but requires additional time to resume the page-fault service routine when the I/O transfer is complete.

In any case, we are faced with three major components of the page-fault service time:

- 1. Service the page-fault interrupt.

- 2. Read in the page.

- 3. Restart the process.

The first and third tasks can be reduced, with careful coding, to several hundred instructions. These tasks may take from 1 to 100 microseconds each. The page-switch time, however, will probably be close to 8 milliseconds. A typical hard disk has an average latency of 3 milliseconds, a seek of 5 milliseconds, and a transfer time of 0.05 milliseconds. Thus, the total paging time is about 8 milliseconds, including hardware and software time. Remember also that we are looking at only the device-service time. If a queue of processes is waiting for the device (other processes that have caused page faults), we have to add device-queueing time as we wait for the paging device to be free to service our request, increasing even more the time to swap.

If we take an average page-fault service time of 8 milliseconds and a memory-access time of 200 nanoseconds, then the effective access time in nanoseconds is